68kMLA Classic Interface

This is a version of the 68kMLA forums for viewing on your favorite old mac. Visitors on modern platforms may prefer the main site.

| Click here to select a new forum. | |

| Anybody here ever run a IIfx with A Tokamac accelerator? | |

| Posted by: Unknown_K on 2016-03-03 12:43:06 Many years ago I snagged a Tokamac IIfx PDS card (2004 ish). The software was vaporware for it so I contacted the original creator (Andrew W Donoho) and he sent me the correct drivers for it. He also told me the IIfx motherboards had defects from the factory with respect to bus mastering so you had to send the IIfx motherboard to get reworked (programmable PAL). From what I remember my IIfx would not boot with the card installed so I never got around to using the drivers. Anyway I figured somebody here might have an upgraded motherboard and I figured it would be a good time to getting all this sorted out before all knowledge is lost. | |

| Posted by: unity on 2016-03-03 20:30:35 Interesting. | |

| Posted by: trag on 2016-03-03 20:34:06 I remember these discussions of old. I hope you find the information you need. Andrew didn't have the code for the PAL? | |

| Posted by: Unknown_K on 2016-03-03 21:15:09 No he didn't. | |

| Posted by: Bunsen on 2016-03-04 06:43:13 Still, that driver that you mentioned would be worth donating to the Mac Driver Museum for posterity. | |

| Posted by: olePigeon on 2016-03-04 08:12:23 If you ever find the PALs or a modified motherboard, you'll have one of the most coveted IIfxes. | |

| Posted by: Unknown_K on 2016-03-05 02:01:18 I can email the driver to anyone who wants it, or wants to send it to an archive. | |

| Posted by: CelGen on 2016-03-05 08:51:01 I've only ever seen a photograph of the card in a book. I have never seen one in person or ever seen one online anywhere. | |

| Posted by: Unknown_K on 2016-03-05 12:25:09 https://photos.google.com/photo/AF1QipMbpYLwGAQaqCn1FzLEHZq9HbZJV09rdoeW0TyM | |

| Posted by: johnklos on 2016-03-05 12:57:30 Unknown_K: that link requires a Google account. Do you think you could post it somewhere that doesn't require people to create an account? | |

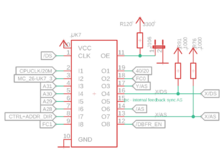

| Posted by: Bolle on 2024-02-14 11:58:27 Digging up this old thread... I just finished writing equations to match the original PAL at UK7. It was quite tricky to figure out and took a while until I catched all possibilities. Here's the signals that are connected to the inputs and outputs:  /DS - data strobe connected to CPU CPUCLK/20M - 20MHz clock signal that drives PDS and I/O devices MC_26-UK7_3 - unknown signal that's output by the memory controller to flag something A31-A28 - address signals connected directly to the CPU bus (aka fast bus) CTRL+ADDR_DIR - controls the direction of the buffers for control and address signals that sit between the "fast" and "slow" busses FC1 - function code bit 1 connected to the CPU /DBFR_EN - output enable signal of the buffers for data between fast and slow busses X-/AS - address strobe originating from a bus master on the slow bus (input or output on the PAL depending on the current bus master) /AS - address strobe originating from bus master on the fast bus, CPU or memory controller - not actually sure if the memory controller can become a bus master or not (input or output on the PAL depending on the current bus master) X-/DS - data strobe connected to devices on the slow bus Y-/AS - address strobe output to bus arbiter PAL and address decoder PAL FC0 - function code bit 0 connected to the CPU 40/20 - tells the memory controller wether to run the CPU at 40MHz or 20MHz And here's the equations with some comments... ;CPU clock switch - low: 20MHz, high 40MHz

/o19 = /i11 ;J106 set

+ /i8 ;ctrl direction: slow-bus to CPU bus

+ /f18 * /f14 * i4 ;!FC0 * !AS * A31 ->0x8000 0000 or higher program space

+ /i9 * /f14 * i4 ;!FC1 * !AS * A31 ->0x8000 0000 or higher data space

+ /i4 * i5 * i6 * /f14 ;!A31 * A30 * A29 * !AS ->0x6000 0000 (slow PDS) or 0x7000 0000 (fast PDS)

+ /i4 * i5 * i7 * /f14 ;!A31 * A30 * A28 * !AS ->0x4000 0000 or 0x5000 0000 ROM or I/O

o19.oe = vcc

;dbuffer.oe

/o12 = /i8 ;ctrl direction: slow-bus to CPU bus

+ /f18 * /f14 * i4 ;!FC0 * !AS * A31 ->0x8000 0000 or higher program space

+ /i9 * /f14 * i4 ;!FC1 * !AS * A31 ->0x8000 0000 or higher data space

+ /i4 * i5 * i6 * /f14 ;!A31 * A30 * A29 * !AS ->0x6000 0000 (slow PDS) or 0x7000 0000 (fast PDS)

+ /i4 * i5 * i7 * /f14 ;!A31 * A30 * A28 * !AS ->0x4000 0000 or 0x5000 0000 ROM or I/O

+ /i4 * /i5 * /i6 * /i7 * i9 * /f14 * f18 ;FC0 * FC1 * /AS * !A31 * !A30 * !A29 * !A28 -> CPU space -> FPU?

o12.oe = vcc

;slow /AS

/f13 = /f14 * /i2 * i3 ;!AS * !C20M * MC_flag

+ /f14 * /i4 * i5 * i6 * i7 ;!AS * !A31 * A30 * A29 * A28 - 0x70000000 fast PDS

+ /f14 * /i4 * /i5 * /i6 * /i7 * f18 * i9 ;!AS * !A31 * !A30 * !A29 * !A28 * FC0 * FC1 - CPU space for FPU

+ /f13 * /f14 ;latch

f13.oe = i8 ;OE: ;ctrl direction: CPU bus to slow-bus

;fast /AS

/f14 = /f13 * /i2 * f15 * i3 ;!X-AS * !C20M * syncAS * MC_flag

+ /f13 * /f14 ;latch

f14.oe = /i8 ;OE: ;ctrl direction: slow-bus to CPU bus

;nc, just for internal purposes - syncAS

/f15 = f13

+ /f15 * /i2

f15.oe = vcc

;slow /DS

/f16 = /i1 * /i2 * i3 ;!DS * !C20M * MC_flag

+ /i1 * /i4 * i5 * i6 * i7 * /f14 ;!DS * !A31 * A30 * A29 * A28 * !AS - 0x70000000 fast PDS

+ /i1 * /i4 * /i5 * /i6 * /i7 * i9 * f18 * /f14 ;!AS * !A31 * !A30 * !A29 * !A28 * FC0 * FC1 - CPU space for FPU

+ /f16 * /i1 ;latch

f16.oe = i8

;/AS to decoder and arbiter PALs

/f17 = /f14

f17.oe = vccI don't know which method the Tokamac uses to become a bus master as there's several different methods. Knowing how the card actually tries to become bus master might give us a hint what's borked in Apples implementation. | |

Posted by: sstaylor on 2024-02-17 19:01:46Digging up this old thread... I just finished writing equations to match the original PAL at UK7.Funny, I just ran across a TokaMac Iici accelerator and have been trying to find the software for it, if there even was any. I saw you had cloned the TokaMac LC. Have you ever come across anything helpful for the Tokamak Iici? | |

| 1 |