68kMLA Classic Interface

This is a version of the 68kMLA forums for viewing on your favorite old mac. Visitors on modern platforms may prefer the main site.

| Click here to select a new forum. | |

| Reverse Engineering the Macintosh IIsi Logic Board | |

| Posted by: demik on 2022-01-24 09:24:34 The Radius NuBus riser has been reversed. It consists of 3 GALs and a bunch of 74LS Chips. JEDEC for the GALs are here : | |

Posted by: Trash80toHP_Mini on 2022-01-24 10:18:47 Thanks so much for linking that treasure! 🙂 Didn't have that nice big pic at hand to post! Now I don't need to ransack two machines for it! Didn't know he uploaded that and the giblets. That'd be the one @nickpunt @joethezombie @Bolle and I were playing with in the Project30 PM skunkworks. In the SE/30 it runs just fine, albeit at only 8MHz. 10MHz NuBus clock is derived in the GALs from 20MHz CPUCLK line on the IIsi PDS. From one of the three NuBus implementations we've now listed, run one or two more NuBus ID lines and interrupts from controller to slots and suddenly it's the same I/O structure as the Macintosh IIci with perfectly matching memory map, HEH! Add 40MHz crystal can to run unsafe at any speed . . . 🤪 | |

Posted by: Melkhior on 2022-01-24 10:24:01The Radius NuBus riser has been reversed. It consists of 3 GALs and a bunch of 74LS Chips. JEDEC for the GALs are here :Are the schematics for the adapter available as well? The GAL content is required but not sufficient to replicate the '030 bus -> NuBus adapter. Edit: Quick'n'Dirty translation of the PAL content to Verilog, never tested if my tool work so YMMV: U12 module GAL20V8A_U12 (

// unused nc1

input i2,

input i3,

input i4,

input i5,

input i6,

input i7,

input i8,

input i9,

input i10,

input i11,

input i13_n,

input i14,

output o15,

output o16,

output o17,

output o18,

output o19,

(* NOREDUCE = "TRUE" *) inout f20,

(* NOREDUCE = "TRUE" *) inout f21,

output o22,

input i23

);

assign o22 = ((i2 | i3 | (~i4) | i13_n) & ((~i2) | (~i3) | (~i4) | i5 | i13_n) & ((~i2) | i3 | (~i4) | (~i5) | i13_n));

assign f21 = ((~i11)) ? ((i2 | i3 | i4 | i5 | i6 | i7 | i9) & (i2 | (~i3) | i6 | i7 | i9) & ((~i2) | i3 | i5 | i6 | i7 | i9) & (i2 | i3 | i23 | i4 | i5 | i6 | (~i9) | (~i14)) & (i2 | (~i3) | i23 | i6 | (~i9) | (~i14)) & ((~i2) | i3 | i23 | i5 | i6 | (~i9) | (~i14)) & (f21 | i8)) : 'bZ;

assign f20 = ((~i11)) ? ((i6 | i7 | i9) & (i23 | i6 | (~i9) | (~i14)) & (f20 | i8)) : 'bZ;

assign o19 = ((i2 | i3 | i4) & (i2 | (~i3) | i4) & ((~i2) | i3 | i4) & ((~i2) | (~i3) | i4 | i5));

assign o18 = ((i2 | (~i3) | i5) & (i2 | i3 | i4 | i5));

assign o17 = ((~i7)) ? i9 : 'bZ;

assign o16 = ((~i7)) ? (((~i2) & (~i3) & (~i5)) | (i2 & (~i3) & (~i5)) | (i2 & i3 & i4 & (~i5)) | (i2 & (~i3) & (~i4) & (~i5)) | (i2 & i3 & (~i4) & (~i5))) : 'bZ;

assign o15 = (((~i7) | i14) & ((~i10) | i13_n));

endmodule // GAL20V8A_U12U13module GAL20V8A_U13 (

input CLK,

input i2,

input i3,

input i4,

input i5,

input i6,

input i7,

input i8,

input i9,

input i10,

input i11,

input OE_n,

input i14,

input i15,

(* NOREDUCE = "TRUE" *) inout f16,

// unused o17,

output o18,

(* NOREDUCE = "TRUE" *) inout rf19,

// unused o20,

(* NOREDUCE = "TRUE" *) inout rf21,

inout f22,

input i23

);

reg rf19_reg = 'b0;

reg rf21_reg = 'b0;

assign f22 = ((~i23) | (~i15) | (~i14));

always @(posedge clk) begin

rf21_reg <= (((~rf21) | rf19) & (rf21 | (~i11)));

end

assign rf21 = (~(OE_n)) ? rf21_reg : 'bZ;

// o20 OE signal is grounded

always @(posedge clk) begin

rf19_reg <= ((i2 | i3 | (~f22) | (~i4) | (~rf21) | i5 | (~i6) | (~rf19) | (~i7) | (~i8) | (~i9) | (~i10)) & (i2 | (~rf21) | (~rf19) | i7 | (~i8) | i9 | (~i10)));

end

assign rf19 = (~(OE_n)) ? rf19_reg : 'bZ;

assign o18 = rf19;

// o17 OE signal is grounded

assign f16 = (rf19 & (i2 | f16));

// i15 OE signal is grounded

endmodule // GAL20V8A_U13U14module GAL16V8A_U14 (

input CLK,

input i2,

input i3,

input i4,

input i5,

input i6,

input i7,

input i8,

input i9,

input OE_n,

(* NOREDUCE = "TRUE" *) inout rf12,

inout f13,

output o14,

(* NOREDUCE = "TRUE" *) inout f15,

(* NOREDUCE = "TRUE" *) inout f16,

output o17,

output o18,

inout f19

);

reg rf12_reg = 'b0;

assign f19 = (rf12 | i6);

assign o18 = ((~i2)) ? (~'b0) : 'bZ;

assign o17 = (((~i2) | f15) & (f16 | (~i7)));

assign f16 = (((~i4) | (~f15) | i8 | (~i9)) & (i3 | f16 | (~i9)));

assign f15 = (((~f13) | (~i9)) & ((~i5) | f15 | (~i9)) & (f15 | i8 | (~i9)));

assign o14 = ((~f19) & i4 & (~i5) & (~f16));

assign f13 = ((~i2) & (~f19) & (~i4) & i9);

always @(posedge clk) begin

rf12_reg <= (~rf12);

end

assign rf12 = (~(OE_n)) ? rf12_reg : 'bZ;

endmodule // GAL16V8A_U14 | |

| Posted by: Trash80toHP_Mini on 2022-01-24 10:41:07 Dunno, @Bolle got that schematic done as well already? Looks like we may have a volunteer? 😉 | |

| Posted by: Trash80toHP_Mini on 2022-01-24 12:17:07 edit: Nice work @Melkhior I rebooted the NuBus in SE/30 project for IIsi Subsystem development and SE/30 specific hack topic for this wonderful tangent! Project30 - fourth edition - Radius IIsi NuBus Adapter build for SE/30?Five years and two days to the date, Project30 is back on the bench thanks to new developments. Replace the IIsi NuBus Adapter in this pic from back then . . . . . . with this card we found at the time . . . . . . add the 40MHz clock from the former to the Radius adapter and...

68kmla.org

68kmla.org

I never got any farther into it after signing off here last September: Project30 - IIsi NuBus adapter in SE/30 trials - take 3Found a tidbit relating to researching the pre-NuChip, discrete component NuBus setup of Macintosh II.1 as well. Might need the ROM upgrade for logic analysis on the board or for comparative testing? One last goodie, The Master/Slave bugaboo of the SE/30 might be addressed using YARC's...

68kmla.org

68kmla.org

| |

Posted by: Melkhior on 2022-01-24 12:53:18edit: Nice work @MelkhiorNot sure about the equations involving registered I/Os (names starting in 'r'), they likely should use the register (that has _'reg' appended in the verilog) rather than the I/O wire as an input. Someone more knowledgeable on GALs would know how to interpret the meaning more accurately. | |

| Posted by: Trash80toHP_Mini on 2022-01-24 13:04:08 OK, cool. Are you a firmware, software or hardware kinda hacker or all three? I find it fun to be mired somewhere in the middle of this kinda thing without being equipped to do much any of it. 🤪 If-n-when @Bolle can find time to do a/o post the Radius schematic, what parts of further development are you comfortable doing? | |

| Posted by: Melkhior on 2022-01-24 23:23:54 @Trash80toHP_Mini SW by trade, got into doing my own hardware for fun and learning during Covid lockdown with the SBusFPGA. Now considering having a got at the NuBusFPGA, so interested in NuBus. I don't have a IIsi so understanding what's needed for a '030 bus -> NuBus adapter is purely intellectual curiosity at this stage - and idly wondering what it would take to be able to 'create' a new NuBus Macintosh from near-scratch (i.e. how many Apple-designed chips are really mandatory to salvage). | |

| Posted by: demik on 2022-01-25 00:53:09 IIRC, @joethezombie worked on this and may have the schematics around | |

Posted by: Trash80toHP_Mini on 2022-01-25 01:38:26Now considering having a got at the NuBusFPGA, so interested in NuBus. I don't have a IIsi so understanding what's needed for a '030 bus -> NuBus adapter is purely intellectual curiosity at this stageLike I said in the Macintosh II Sadness thread, have a look at Apple's NuBus primer: https://vintageapple.org/inside_o/pdf/Designing_Cards_and_Drivers_for_the_Macintiosh_II_and_SE_1987.pdf The Radius adapter seems like black magic, maybe more like the PAL based Macintosh II implementation that's the subject over there? The Apple Adapter for IIsi and the DuoDock's NuBus interfaces are implemented in just the Controller, Two Transceivers and a 40MHz Clock. So simple, but the Radius adapter seems more simple than that? @demik I'm hoping joe or Bolle will have done that schematic already, but haven't heard from either about it. I'd love to get started on that project again. | |

Posted by: Melkhior on 2022-01-25 10:05:38Like I said in the Macintosh II Sadness thread, have a look at Apple's NuBus primer:I have all the relevant PDFs and a paper copy of the 3rd edition on the way ;-) Currently hesitating to have the (very) expensive design manufactured - I have a simulation telling me if the hardware works I should be able to talk to the NuBus, but I'm not sure about all the critical bits (interfacing the CPLD/FPGA/driver chips to the NuBus & the VGA/HDMI stuff) being well designed schematics-wise... and anyway with CNY coming up there's no point in ordering anything before mid-february. And all the chips might not be available anyway with the ongoing shortage (I've had to fix a few references already, but more keep disappearing). And quite expensive just to figure out if can be made to work - last time I checked, a couple of boards would set me back close to 600€ once the custom duty is taken into account... | |

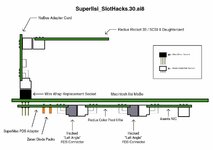

| Posted by: Trash80toHP_Mini on 2022-01-25 10:36:13 AHA, so you're rebooting the @dlv HDMI on NuBus thread! NuBus expansion via FPGA->NuBus Slot is very cool. Can you flip it around to do PDS to NuBusFPGA Slots adapter? ISTR doing anything like that runs into the lack of I/O lines on available FPGA parts? At only 20-33MHz might you be able to get around that limitation by adding a second MUX between FPGA and PDS? OMG, whatta kluge that would wind up being! 😱 MUX between PDS and FPGA would yield higher freq expansion card I/O though, no? I've been thinking a 10/100 NIC on a fast PDS might be worthwhile as opposed to disappointing 10MHz NuBus bottlenecked NIC performance reports? _________________________________________________________________________________________________ Meanwhile, I located the SuperIIsi™ project box. Promised pic:  | NuBus Adapter/FPU | TwinSlot PDS Adapter | Isi Logic Board |Per DuoDock implementation, add second NuBus Slot to adapter with a PDS passthru atop for 030 NIC? Do it up right with three NuBus Slots and a Passthru that's either/or by sharing the Top NuBus Slot's interrupt? Now you see why climbing the ladder in the SE/30 form factor will be a lot more flexible that expanding I/O within the confines of the sleek, low profile IIsi case. Unless of course . . .  @Danamania is the 'fritter Vhack muse as well. | |

Posted by: joshc on 2022-01-25 10:50:54Meanwhile, I located the SuperIIsi™ project box. Promised pic:Is that a new/current pic? Please tell me you are going to recap that board soon. Note the PDS adapter has a nasty leaky cap too. 🙂 | |

| Posted by: Trash80toHP_Mini on 2022-01-25 11:39:13 That's my DOA board, I took the sticker off for the copystand session today. It's the logic board that bangs around the joint, in and out of the project box, gets buried under heaps of crud on the bench and travels back and forth to work with me whenever I feel like playing with it in downtime. I have no regard for it in terms of static discharge whackage. 😛 It was supposed to be an in box replacement board, but wound up being the replaced board. Now I've got more stuff to do, I should go through all my Macs to decap/clean them up even if I can't find the time to recap anything anytime soon. THX for the heads up on the TwinSlot adapter! edit: I see it now, it's the can on the NuBus adapter? IIsi boards: the DOA board, one recapped board and several to locate for inspection. I only have two cases, maybe five or six boards in total? No working PSUs, but the SuperIIsi™ requires a lot more power than the stock PSU to run a pair of PDS cards, Rocket 33, its SCSI II Daughtercard ans a Savvio Server Drive.. | |

| Posted by: Trash80toHP_Mini on 2022-01-26 08:16:30 Gotta get this one onto the same page as the maniac's IIsi vHack:  I've since learned that what I thought were noise reducing Zener Diodes should be labeled Resistor Packs (for bus termination?) on the SuperMac VidCard adapter. My adapters don't have packs installed, but I've seen pictures of same where they were installed. Those were orange as depicted, is there a color coding standard for SIP components. Riser PCB for IIsi in SE/30 or Dana's IIsi design expansion would approximate Max SE/30 PDS card spec or full height like the A/B so PDS passes through aligned with the IIsi backplane plate. I wonder about the physical config of the two machines in terms of breakout panel, I wonder if it's the same? At any rate, the expansion would be a vertical ladder with stepped adapters. Gotta have room for an 040/601 accelerator card adaptater on there as well. @Danamania I'm thinking a replacement IIsi version of this amalgam with the SE/30 riser kluge should be installed in a printed case along the lines of your Snow White Cubes? Machining clear plexi would be the way I'd do it, to heck with RFI generation concerns for this puppy. SE/30 version is obviously going into my clear SE/SE/30 prototyping case. 🙃 | |

Posted by: Trash80toHP_Mini on 2022-01-26 08:33:44I've since learned that what I thought were noise reducing Zener Diodes should be labeled Resistor Packs (for bus termination?) on the SuperMac VidCard adapter. My adapters don't have packs installed, but I've seen pictures of same where they were installed. Those were orange as depicted, is there a color coding standard for SIP components.Thinking about it, SuperMac riser is for a max size SE/30 VidCard. What might the differentiation between IIsi and SE/30 PDS slots be for them to have made provision for those packs? | |

| Posted by: Trash80toHP_Mini on 2022-01-27 11:22:38 Credit where credit is due time. Got this PM from @nickpunt November, 2018: Hey Trash,We had @joethezombie saying he hated us for having been roped into buying it by the third post of that 249 reply PM thread! Anyway, if the Radius fork of Project30 pans out, you'll know where the props belong! Many thanks nick. 🙂 | |

| Posted by: nickpunt on 2022-01-28 01:53:16 Well it all started with your thought experiments @Trash80toHP_Mini ! Exciting to see this come together and potentially unlock a whole "new" set of options on SE30 with nubus. Spotting that radius board on eBay was a bit like that Asimov quote: The most exciting phrase to hear in science, the one that heralds new discoveries, is not “Eureka” but “That's funny...” | |

| Posted by: Trash80toHP_Mini on 2022-02-23 12:32:42 Thanks for that, nick. Asimov rocked! Just wish I could pull off one of these insane projects. Started a riff on this and another project today. EuroDin Slot connectors are so last year's fashion, expensive and worse when you need to buy the matching plug in that form factor. 😉 They're fine for the connectors above when it's plug in time. MagicalBus™ on the universal 64-bit PCI Connector would be my answer for NuBus slot riser and general purpose adapter for the SE/30 tower of cards' foundation. MagicalBus™ - PDS reimagined in 68000/68020/68030 compatible form.Been playing around with reverse engineering boards here and there and something twisted up in my head this morning. Inspiration would be the Radius Magic Bus™ setup for the SE with FPD and TPD cards: Pie hole in the front is too constraining for reverse engineered boards headed into the...

68kmla.org

68kmla.org

That one was LCIII project inspired. The SE chassis is soooooo infuriatingly constraining. 🙄 | |

| Posted by: The Salami Boss on 2022-03-05 00:30:31 I've got a spare (but catatonic) IIsi board I can forward to any interested parties if that would be in any way helpful. It has booted within the last year, but currently only either white-screens or death chimes in early boot. I assume it just needs a recap but I have a recapped board already so perhaps my laziness can be your gain. | |

| < 3 > |