68kMLA Classic Interface

This is a version of the 68kMLA forums for viewing on your favorite old mac. Visitors on modern platforms may prefer the main site.

| Click here to select a new forum. | |

| Please help me figure out what the deal is with this IIx RAM | |

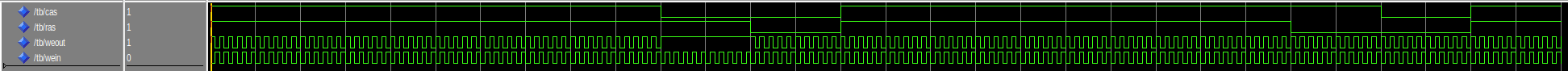

| Posted by: tattar8 on 2020-06-17 03:52:02 I threw together some VHDL to simulate the circuit design. Does this behavior look correct?  | |

| Posted by: Bolle on 2020-06-17 04:35:58 Looks good, but you want to make sure that the time between /ras going low and /weout going low is greater than the test mode setup hold time of the chips on your SIMMs. With a modern CPLD or FPGA this is an easy thing to implement in the logic. With a GAL or discrete logic you will have to use chips that have long enough propagation delays. | |

| Posted by: tattar8 on 2020-06-17 04:44:02 Could I just throw a series of noninverting buffers on the /weout to introduce some propagation delay? | |

| Posted by: tattar8 on 2020-06-18 06:18:03 The Mac II has separate CAS and RAS lines going to each SIMM. Does that mean that all the banks are getting refreshed independently? Or can I assume that while accesses may occur at different times, the CAS-before-RAS refresh will always be synchronized? If they're completely independent, then I'll need to build the whole design 4 times, which would make it impractical to just use 74 series logic, and instead actually find a CPLD or FPGA and appropriate level shifting hardware (since all the ones I can find run at 3.3v). | |

Posted by: trag on 2020-06-18 13:46:11and instead actually find a CPLD or FPGA and appropriate level shifting hardware (since all the ones I can find run at 3.3v). Atmel and Altera still have 5V CPLD lines available. Atmel was bought by Microchip. https://www.microchip.com/design-centers/fpgas-and-plds/splds-cplds | |

| Posted by: tattar8 on 2020-06-21 15:12:57 Do you know of any ready-made development boards for Atmel/Microchip's CPLD lines? I can't find any, and I really don't want to spin my own board for one at this point. I built a circuit based on the VHDL code that generated the waveform I posted earlier, but while it didn't stop the machine from booting normally, it still didn't allow larger RAM sizes. @Bolle Did I completely overcomplicate this? Does the GAL's logic for the WE not worry about CAS-before-RAS at all, and instead just holds WE high whenever RAS is high regardless of what CAS is doing? So this whole thing boils down to simply "RAS * WE", which I can just build using a single AND gate? | |

| Posted by: chiaki on 2020-06-24 02:11:32 micron produced actually 1Mx4 DRAM ICs without JEDEC testmode implemented. like mt4c4005 and "newer" produced DRAM also dont have the jedec testmode in the datasheet also found a detail description about the difference in the datasheet, maybe it help  | |

| Posted by: Bolle on 2020-07-08 17:31:49 Following the SE/30 schematics it should be possible to implement the same simple logic into the Mac II logicboard. The independent RAS lines going to the SIMMs originate from the same two RAS signals coming out of the GLU gate array just like the SE/30. Everything that should need to be done on the Mac II is grabbing those signals somewhere from the logicboard and feed them into a GAL: -R/W - UG7 17/GLU 52/ -RAS.A - GLU 78/UH14 2&4 -RAS.B - GLU 79/UH14 6&8 -CAS.LL - GLU 80/UH14 11 (original) or 5 (buffered) (all the CAS signals should be the same, otherwise the SE/30 approach would not work and it's using the same GLU gate array) Then we remove R19 and R23 on the back of the logicboard to cut the traces between the buffer UG7 and the /WE pins on the SIMM sockets. We will have to inject our new /WE signal either into two vias next to the battery or next to UG7 where the two resistors have been before. In the GAL we just make sure /WE to the SIMMs only gets activated when the accompanying RAS signal is active and keep it latched as long as RAS is there, no matter what R/W is doing from then on. This hack is completely reversible, just remove the wires you tapped into places and solder the two resistors back on. I am going to try this on a Mac II logicboard I just got after I finish recapping it and will report back. | |

| Posted by: Phipli on 2020-07-16 01:19:36 Very interested in this. These look easy to copy if you could get the timing right : https://www.worthpoint.com/worthopedia/4x-4mb-apple-mac-ii-iix-30pin-tin-non-1825526434 Thats a quad or isn't it? | |

| Posted by: Phipli on 2020-07-18 05:52:47 Dumb question... if the II and IIx are in part slow because they were designed for 120ns RAM and have a large number of wait cycles... if you have faster RAM is it possible to change the number of wait cycles in the ROM, for example with a ROMinator? | |

| < 2 |