68kMLA Classic Interface

This is a version of the 68kMLA forums for viewing on your favorite old mac. Visitors on modern platforms may prefer the main site.

| Click here to select a new forum. | |

| Carrera040 cloning | |

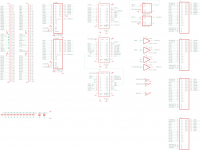

| Posted by: Bolle on 2020-04-14 07:18:36 The topic of cloning the cache card for the Carrera040 came up in another thread so I would like to gather some information here to push this forward. First off: can someone tell me what kind of connector they used and if I can get one (or an equivalent) somewhere?    We're looking for something with 1.27mm of pitch and 2 rows of 50 pins. Preferably should match the original pad spacing so I can keep the original layout:  Schematics so far:  Working on finishing the board routing and getting the GALs cracked right now. | |

| Posted by: mdeverhart on 2020-04-14 08:19:21 Samtec has a line of connectors that look very similar (if not identical) to those: https://www.samtec.com/connectors/micro-pitch-board-to-board/050/strips | |

| Posted by: jessenator on 2020-04-14 08:56:07 Yeah, same connector on some versions of the ATi Mach64 for the VRAM expansion cards it seems:  Looks like mdeverhart is on the right track there. | |

| Posted by: Solvalou on 2020-04-16 14:22:39 They definitely don't look like they would be easy to source, I hope I'm proven wrong. If you do score a load, how do you hope to solder them on? Looks like it would be a real bugger to do by hand. | |

| Posted by: demik on 2020-04-21 11:31:38 Looks like a simple 1.27 PCB connector would match. Here is the male version : https://www.ebay.fr/itm/20Pcs-50-Position-1-27mm-Pitch-Double-Row-Straight-Pin-Header-Strip/183740371764?_trkparms=ispr%3D1&hash=item2ac7c79334:g:3TIAAOSwDdxekLxI And the female version : https://www.ebay.fr/itm/1-27mm-Pitch-Double-Row-Female-Pin-Header-Socket-PCB-Connector-Strip-Breadboard/264126328363?hash=item3d7f27ee2b:m:mE74SeHI5VG6g-Ly1mUua_g They are fairly cheap so it's worth a shot I guess. | |

| Posted by: Bolle on 2020-04-28 12:50:15 Going to have to see if I can fit through hole mounted connectors in place. The original (and the PCB I routed so far) uses a SMD connector. I will have to check if there is enough space. Also I advanced on the GAL front. Was able to read out something from all three of them but two fusemaps won’t disassemble into equations using opaljr. The one that does convert into equations looks fine. Didn’t have time today to burn the extracted fusemaps onto new chips yet. I will do that tomorrow to verify if the fusemaps are valid. | |

| Posted by: Bolle on 2020-04-29 08:51:35 GAL copies confirmed:  Jedec files, equations and schematics attached. I'll order a set of test boards once I finish something else that I am working on to save shipping costs. If someone wants to make themselves a board in the meantime let me know and I'll send gerber files along.  View attachment U1_1.jed.jed View attachment U1.EQN View attachment U2_syn_ac_correct.jed View attachment U2.EQN View attachment U3_syn_ac_correct.jed View attachment U3.EQN View attachment Cachecard.sch | |

| Posted by: Bolle on 2020-06-07 17:42:01 I have a set of 5 prototype boards on the way together with some other exciting stuff. Once the boards are confirmed to work I will share the gerber files (and pass on the remaining 4 proto boards that I don't need - in case they do work) | |

| Posted by: AlpineRaven on 2020-06-07 19:41:44 Oooooh! Following! Cheers AP | |

| Posted by: olePigeon on 2020-06-08 01:41:28 Ooooooooo. Awesome work! | |

| Posted by: Bolle on 2020-06-30 19:35:40 Looking good...   On one of my Carreras the cloned cache card would not be stable with 40MHz. Everything is fine at 33MHz though. After some back and forth it turned out that not all combinations of CPU and cachecard will run at 40MHz. I swapped around different CPUs and even found a combination where the original cachecard would refuse to work resulting in a hard crash once the Carrera INIT loads. I will be revising the PCB design a little and then post the gerbers and a BOM so everyone can build their own cachecards. | |

| Posted by: Bolle on 2020-07-01 16:36:00 Gerbers attached. BOM -C1-C11: 0.1uF 1206 ceramic caps -C12, C13: 22uF/10V tantalum or electrolyte caps -R1: 330Ohm -R2, R3: 220Ohm ->pad size is metric 1206 for all the above resistors and caps -U5-U8: 32K x 8 SRAM 15ns SOJ (IS61C256AL-15JL, IDT71256SA15 and the like) -U9, U10: 8K x 8 TAG SRAM 12ns SOJ (ATT7C174J-12, IDT71D74S12... only exists as NOS, no modern replacement) -U1: GAL20V8 10ns (7ns works as well) PLCC28 -U2, U3: GAL20V8 7ns PLCC28 -U11: 74F74 SO14 -U12: 74F125 SO14 -J1: 1.27mm pitch 2 x 50 SMD pin headers View attachment cachecard.zip | |

| Posted by: AlpineRaven on 2020-07-01 18:39:30 Looking forward to it! Cheers AP | |

| Posted by: Solvalou on 2020-07-02 01:06:07 Oh this is looking fantastic! Hats off to you sir, I have no idea how you pulled this off but you have. Will be following closely and hopefully will take one of these for my Cache-less one in my IIci if you ever sell one. Pretty sure mine's a 40MHz one so not sure if I will have some stability issues my end. Might be worth compiling a list of tested CPU's. | |

| Posted by: Unknown_K on 2020-07-02 06:55:50 How many people actually own a Carrerra? I have one with cache if my memory is correct. | |

Posted by: TimHD on 2020-08-09 18:24:38How many people actually own a Carrerra? I have one with cache if my memory is correct.I have one. I think it’s in one of my IIci or se/30s. Pretty sure it didn’t come with a cache card. | |

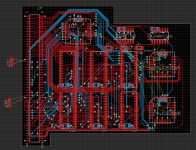

| Posted by: Bolle on 2021-01-07 00:42:02 Well, now that we've got cachecards the obvious thing to do was making accelerators to have something to plug all those cache cards into:   View attachment U7.jed View attachment U12_CarreraPROM_1FD8.bin | |

| Posted by: Bolle on 2021-01-07 05:19:21 Ugh, images messed up in the post above... only noticed I hadn't attached them on here but linked them to imgur right after the editing window went out. Anyways:  View attachment C040.png | |

| Posted by: K Trueno on 2021-01-07 06:40:30 Wow, a Carrera040 clone, now you are talking :-D | |

| 1 > |